Cysicを解読する:ハードウェアアクセラレーションとZKマイニングの台頭前夜

TechFlow厳選深潮セレクト

Cysicを解読する:ハードウェアアクセラレーションとZKマイニングの台頭前夜

CysicはZKの大規模採用というビジョンの実現をどのように支援するのか?

執筆:Nickqiao & 霧月、Geek web3

今年4月、Vitalikが香港ブロックチェーンサミットを訪問し、「Reaching the Limits of Protocol Design」と題した講演を行った。その中で、イーサリアムのDankshardingロードマップにおいてZK-SNARKsが示す可能性について再言及するとともに、ASICチップがZKの高速化に与える大きな貢献についても展望した。

以前より、Scroll共同設立者の張燁氏は、ZKの従来分野における応用範囲はWeb3内よりも広い可能性があると指摘している。信頼できる計算、データベース、検証可能なハードウェア、コンテンツ改ざん防止、zkML(ゼロナレッジマシンラーニング)など、ZKに対する需要は多岐にわたり、リアルタイムでのZK証明生成が実現すれば、Web3と伝統的産業双方にパラダイムシフト級の変革がもたらされるだろう。しかし、効率性や経済コストの観点から見ると、現在の技術ではZKの大規模普及にはまだ遠いのが現状である。

実際、2022年にはトップVCのa16zやParadigmが公開レポートを通じて、ZKハードウェアアクセラレーションの重要性を明確に表明していた。Paradigmに至っては、「将来のZKマイナーの収益はビットコインやイーサリアムマイナーと肩を並べるようになるだろう。GPUやFPGA、ASICに基づくハードウェアアクセラレーションソリューションには巨大な市場ポテンシャルがある」と断言している。その後、ScrollやStarknetといった主要ZK Rollupの盛り上がりとともに、ハードウェアアクセラレーションは一時的に市場の注目を集めるキーワードとなり、Cysicなどのプロジェクトがリリースに近づくにつれて、その熱気はさらに高まっている。

我々はこう断じることができる。ZKに対する巨大な需要を背景として、ZKマイニングプールやリアルタイムZKP生成のSaaSモデルによって新たな産業チェーンが開拓され得る。この潜在力を持つ新大陸において、実力を持ち先発優位性を備えたZKハードウェアベンダーは、次世代のBitmain(比特大陸)となる可能性を秘めているのだ。

ハードウェアアクセラレーション分野において、Cysicは最も注目を集める有力プレイヤーの一つである。同チームは有名なZKP技術競技プラットフォーム「ZPrize」の主要賞を受賞しており、2023年からはZPrizeのメンターとしても活動している。また、BtoB向けZKマイニングプールおよびBtoC向けZK-DePINハードウェアという戦略的製品ラインアップにより、Polychain、ABCDE、OKX Ventures、HashkeyといったトップVCから総額約2000万ドルの大型資金調達を成功させた。

7月末のCysicテストネットのリリースとZKマイニングプールのオープンを目前に控え、各コミュニティにおけるCysicへの関心が高まりつつある。本稿では、より多くの人々がCysicの製品原理やビジネスモデルを理解できるようにするとともに、ZKハードウェアアクセラレーションの基本的な仕組みについて簡単に解説する。以下では、Cysicに関する知識を簡潔に要約し、理解のハードルを下げることを目指す。

ZK証明システムをプロセスから理解する

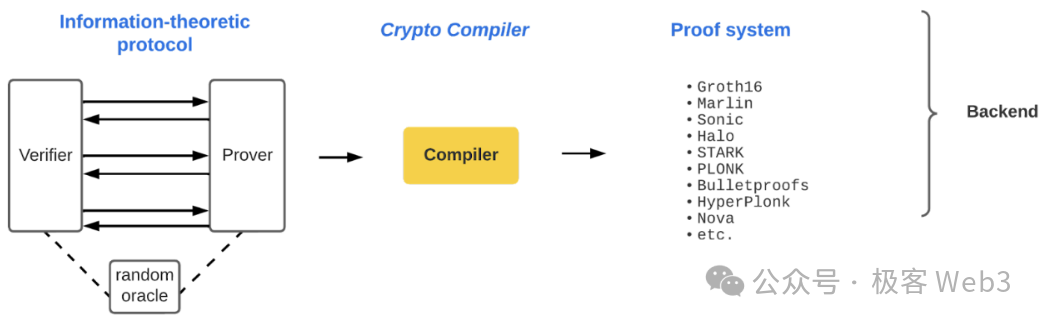

ZK証明システムは非常に複雑だが、大まかな構造を理解するには、役割と処理プロセスの視点から分解するのが有効である。一般的な計算をZK化するシステムの場合、そのコアプロセスは以下の通りである。

まず、フロントエンドを通じてZKシステムとやり取りを行い、証明対象となる内容を提出する。フロントエンドはこれを適切な形式に変換し、ZK証明システムが処理しやすいようにする。その後、特定の証明システムまたはフレームワーク(Halo2、Plonkなど)を用いてZK証明を生成する。このプロセスは次のステップに細分化できる。

1. 問題設定:まず、何を証明するかを明確にする。例えば、「証明者Proverはあるデータを知っている/持っている」と主張するケース。「方程式F(x)=wの解Nを知っている」という主張を示したいが、Nの値自体は他者に見せたくない。

2. 算術化とCSP:証明者が証明内容を提出すると、システムはそれを等価に表現する数学モデル/プログラムを構築し、フォーマット変換を行うことで証明システムが扱える形にする。具体的には、「方程式F(x)=wの解Nを知っている」という主張は、元の数式から論理ゲート回路や多項式の形へと変換される。

3. 次に、HaloやPlonkなどの適切な証明システムを選択し、前述のステップで生成された内容をコンパイルして利用可能なZKPプログラムを作成する。証明者はこのZKPプログラムを使って証明を生成し、検証者に送付して検証を依頼する。

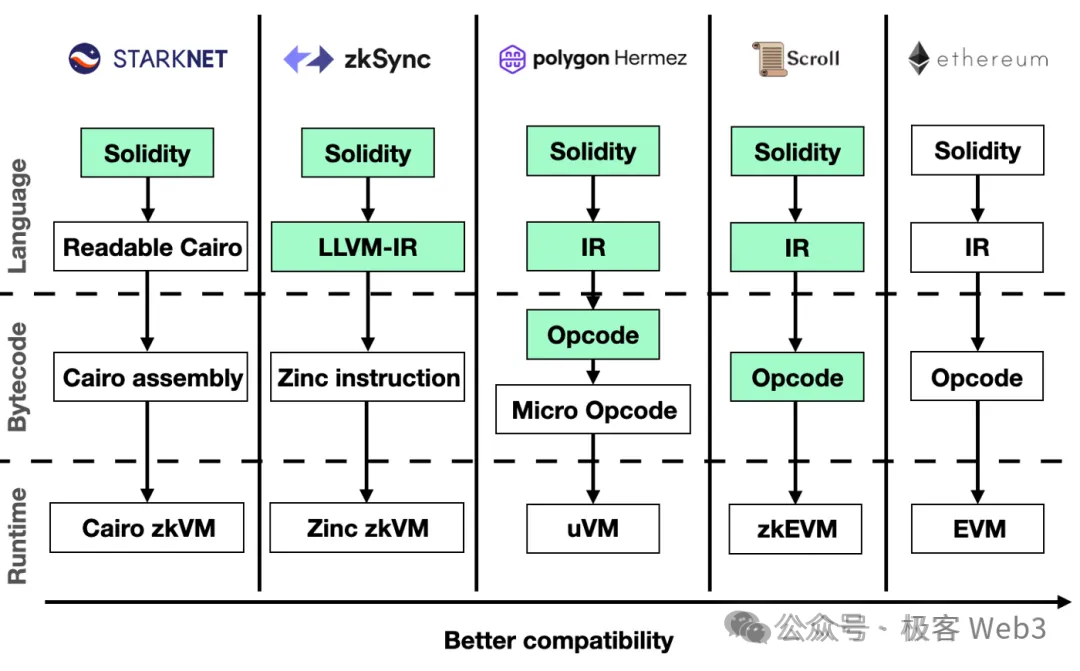

zkEVMのようにイーサリアムL2で頻繁に使われるZKシステムは、本質的にスマートコントラクトをEVMの低レベルオペコードにコンパイルし、それぞれのオペコードを論理ゲート回路/多項式制約の形式に変換した後、バックエンドのZK証明システムで処理する。

なお、現在ブロックチェーンで広く使われているZKP技術は主にzk-SNARK(ゼロナレッジ簡潔非インタラクティブ知識証明)であり、ZK Rollupの多くはSNARKの「簡潔性」を活用しており、「ゼロナレッジ性」ではない。「簡潔性」とは、ZKPが非常に小さなサイズ(数百バイト程度)に圧縮でき、検証コストが極めて低いことを意味する。

これにより、ProverとVerifier間の作業量は非対称的になる。Proverが証明生成に高いコストを負担する一方、Verifierの検証コストは非常に低くなる。この非対称性をうまく活用し、「1人のProver、複数のVerifier」というシナリオでZKを採用することで、全体のコストをProver側に集中させ、Verifier側のコストを大幅に削減できる。これは分散型検証にとって極めて有利であり、まさにイーサリアムL2の設計思想である。

ただし、この検証コストをZK生成側に転嫁する方式は万能ではなく、ZK Rollupプロジェクトにとって証明生成にかかる高コストは最終的にUXや手数料に再び転嫁され、長期的な発展を妨げる可能性がある。

ゼロトラストおよび分散型検証の場面でZKが大きな力を発揮するとはいえ、生成時間のボトルネックに起因して、現時点ではzkEVM、zkVM、ZK Rollup、ZKブリッジいずれも大規模導入の経済的基盤を欠いている。

このような課題に対応するため、Cysic、Ingonyama、IrreducibleといったZKアクセラレーションプロジェクトが登場し、それぞれ異なるアプローチでZKP生成コストの削減に挑んでいる。以下では、技術的観点からZKP生成の主な負荷とアクセラレーション手法、そしてなぜCysicがZKアクセラレーション分野で大きなポテンシャルを秘めているのかを解説する。

計算負荷:MSM と NTT

多くの人が知るように、ZKPのProverによる証明生成には非常に長い時間がかかる。ZK-SNARKプロトコルではよくあることだが、Verifierは1秒で証明を検証できる一方、Proverにとっては半日から1日以上かかる場合もある。ZKPによる計算を効率的に使うには、従来のプログラム形式をZKフレンドリーな形式に変換することが不可欠である。

現在、この変換には二つの方法がある。一つはHalo2のような証明システムフレームワークを使って回路を記述すること。もう一つはCairoやCircomといったドメイン固有言語(DSL)を使い、計算を中間表現に変換し、後に証明システムに渡す方法である。証明システムは、記述された回路またはDSLでコンパイルされた中間表現に基づいてZK証明を生成する。

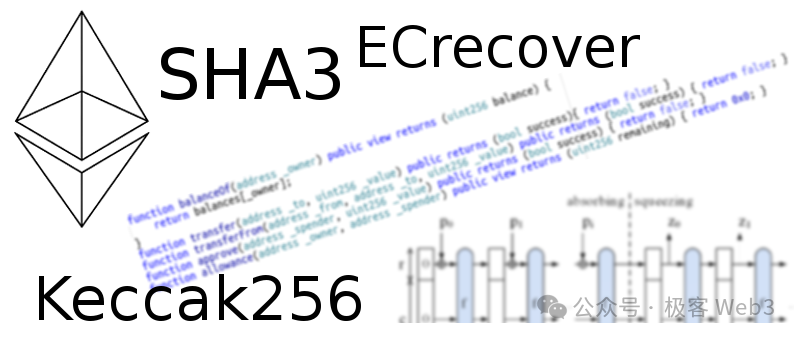

プログラム操作が複雑になればなるほど、証明生成に必要な時間も長くなる。また、ある種の操作は本質的にZKに不向きであり、それらを実装するには追加の工数が必要となる。例えばSHAやKeccakハッシュ関数はZKPに不向きであり、これらを使用すると証明生成時間が延びる。また、従来のコンピュータ上で実行コストが低い操作でも、ZKPにとっては不利な場合がある。

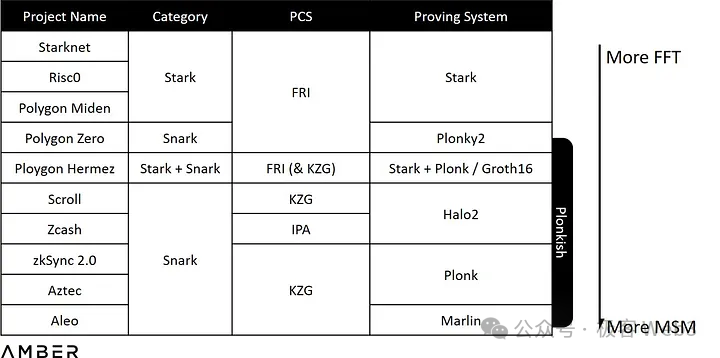

ZKに不向きな計算タスクを除いても、ZK証明生成プロセスは使用する証明システムによって異なるものの、そのボトルネックは本質的に類似している。ZK証明生成において最も計算リソースを消費するのは、MSM(Multi-Scalar Multiplication)とNTT(Number Theoretic Transform)の二つである。これらの計算は、証明生成時間の80~95%を占める。正確な割合はZKPのコミットメントスキームや実装方法に依存する。

MSMは楕円曲線上のマルチスカラー乗算を扱い、NTTは有限体上のFFT(高速フーリエ変換)であり、多項式乗算の高速化に用いられる。異なるスキームの組み合わせにより、FFT/MSMの負荷比率は変化する。

例としてStarkを取り上げると、そのPCS(Polynomial Commitment Scheme:多項式コミットメントスキーム)にはKZGやIPAで使われる楕円曲線ではなく、ハッシュに基づくFRIが用いられているため、MSM計算はまったく存在しない。表の上に行くほどFFT演算が多く、下に行くほどMSM演算が多くなる。

最適化手法

MSM演算は予測可能なメモリアクセスを伴うため、大量の並列化が可能だが、大量のメモリ資源を消費する。また、並列化してもスケーラビリティに課題があり、依然として遅くなる可能性がある。そのため、MSMはハードウェア上で加速可能だが、膨大なメモリと並列計算資源を必要とする。

一方、NTTはランダムなメモリアクセスを伴うためハードウェアに不向きであり、分散型インフラでも処理が難しい。NTTが分散環境で実行されると他のノードのデータにアクセスせざるを得ず、ネットワーク通信が発生することで性能が大きく低下する。

そのため、データの格納と移動が主要なボトルネックとなり、NTTの並列化能力を制限する。NTTのアクセラレーションの大部分は、計算とメモリの相互作用の管理に集中している。

実は、MSMとNTTの効率ボトルネックを解決する最も簡単な方法は、これらの操作を完全に排除することである。最近提案されたHyperplonkなどの新しいアルゴリズムは、Plonkを修正してNTTを排除している。これによりHyperplonkは加速しやすくなるが、代わりにsumcheckプロトコルといった新たなボトルネックが生じる。同様にSTARKアルゴリズムはMSMを必要としないが、FRIプロトコルが多数のハッシュ計算を導入してしまう。

ZKハードウェアアクセラレーションとCysicの究極目標

ソフトウェアおよびアルゴリズムレベルの最適化は重要かつ価値があるが、明らかな限界がある。ZKP生成効率を十分に最適化するには、ハードウェアアクセラレーションが必須であり、これはASICやGPUがBTCおよびETHのマイニング市場を支配したのと同じ流れである。

問題は、「ZKP生成を加速する最適なハードウェアとは何か?」ということだ。現在、ZKアクセラレーションにはGPU、FPGA、ASICなど複数のハードウェアが使用可能であり、それぞれに長所と短所がある。

これらを比較してみよう。

まず、開発面での違いを簡単な例で説明する。例えば、単純な並列乗算を実装したいとする。

-

GPUの場合、CUDA SDKが提供するAPIを使えば、ネイティブコードのように開発でき、並列計算能力を獲得できる。

-

FPGAの場合、ハードウェア記述言語を新たに学ぶ必要があり、この言語を使ってハードウェアレベルの接続を制御し、並列アルゴリズムを実現する。

-

ASICの場合、チップ設計段階でトランジスタの接続配置が固定され、その後変更できない。

これらの選択肢にはそれぞれ利点と欠点があり、ZK分野の発展段階に応じて適したものが異なる。CysicはZKハードウェアアクセラレーションの究極的ソリューションとなることを目指しており、その段階的戦略は以下の通りである。

-

GPU向けSDKを開発し、ZKアプリケーションにソリューションを提供するとともに、ネットワーク全体のGPUリソースを統合する。

-

FPGAの柔軟性とバランスの良さを活かし、カスタマイズされたZKハードウェアアクセラレーションを迅速に実現する。

-

独自開発のASICベースZK DePINハードウェアを展開する。

-

Cysic NetworkはSaaSプラットフォーム/マイニングプールとして、ZK DePINとGPUの全計算リソースを統合し、ZK業界全体に計算力と検証ソリューションを提供する。

以下では、複数のサブセグメントに分けながら、ZKアクセラレーションソリューションの差異とCysicの戦略を深く理解していく。

ZKマイニングプールとSaaSプラットフォーム:Cysic Network

ScrollやPolygon zkEVMといった有名なZK Rollupも、それぞれのロードマップで「非中央集権的なProver(去中心化Prover)」の概念を明確に掲げており、これは実質的にZKマイニングプールの構築を意味している。この市場主義的なアプローチにより、ZK Rollupプロジェクトは負担を軽減でき、マイナーおよびマイニングプール運営者がZKアクセラレーションソリューションの最適化を継続的に推進するインセンティブが生まれる。

Cysicのロードマップには、Cysic Networkと名付けられたZKマイニングプールおよびSaaSプラットフォーム計画が明記されている。これはCysic自身の計算リソースを統合するだけでなく、マイニング報酬を通じてサードパーティの計算リソース(余剰GPUや一般ユーザーのzk DePINデバイス)も吸収する。

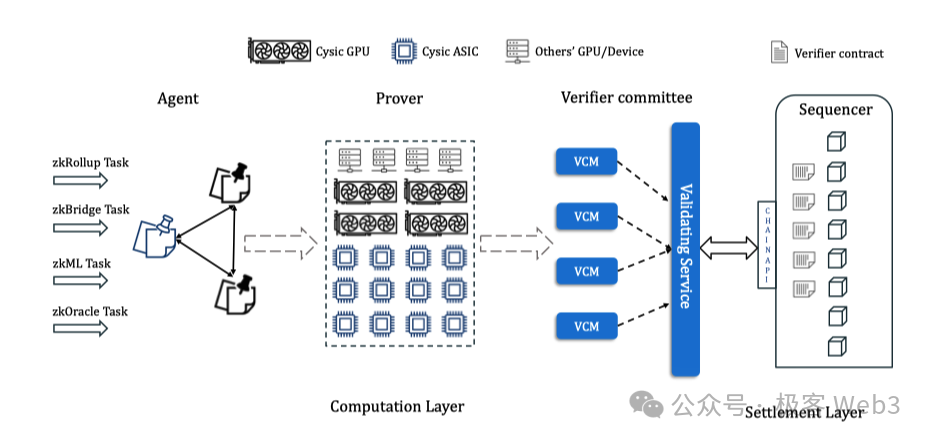

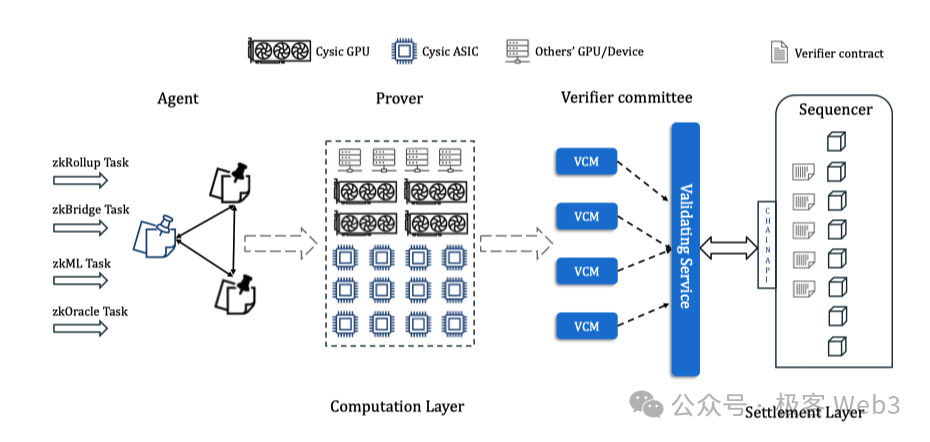

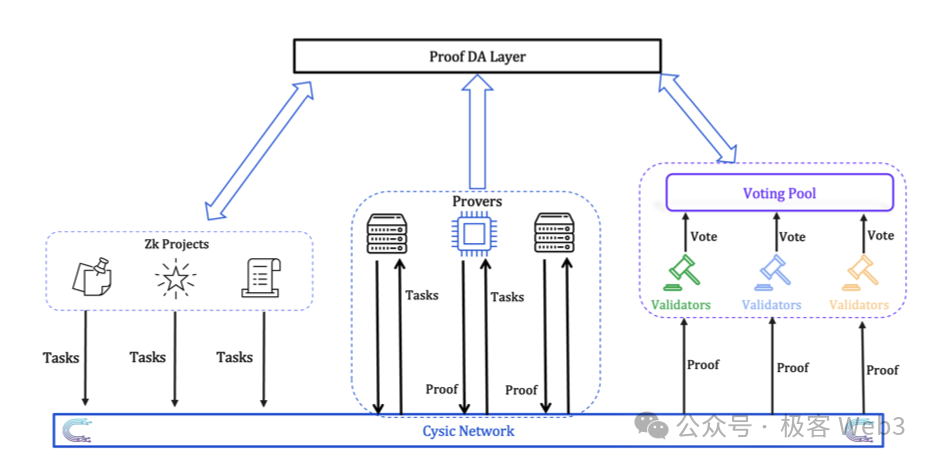

その全体的な検証ワークフローは以下の通りである。

-

ZKプロジェクトが証明生成タスクを代理人(Agent)に提出する。Agentの役割は、証明タスクを検証ネットワークに転送すること。初期段階ではCysic公式がAgentを運営し、将来的には資産ステーキングを導入して誰でもAgentになれるようにする。

-

-

Proverが証明タスクを受け取り、ハードウェアを使ってZK証明を生成する。Proverはタスクを請け負うためにトークンをステーキングし、タスク完了後には報酬を得る。

-

-

検証者委員会がProverが生成した証明の有効性を検査し投票する。一定票数に達すると証明は有効とされる。検証者はトークンをステーキングして委員会に参加し、投票に貢献することで報酬を得る。このプロセスはEigenLayerのAVS(Actively Validated Services)概念と組み合わせ、既存のRestakingインフラを再利用できる。

詳細な相互作用プロセスは以下の通り。

上記のプロセスには一点注意が必要だ。資産ステーキング、報酬配布、計算タスクの提出といったすべてのアクションは、専用プラットフォームに依存しており、それには専用のブロックチェーンインフラが必要となる。

そのため、Cysic Networkは独自のパブリックチェーンを構築しており、特有の合意アルゴリズム「Proof of Compute(PoC)」を採用している。その基本原理は、VRF関数とProverの過去の実績(デバイスの可用性、証明提出回数、証明の正答率など)に基づき、ブロック生成者を選出するというものである(ここでの「ブロック」は各デバイスの情報記録およびトークン報酬配布の用途)。

もちろん、ZKマイニングプールおよびSaaSプラットフォーム以外にも、CysicはGPU、FPGA、ASICといった異なるハードウェアに基づくZKアクセラレーションソリューションに大規模に投資している。次に、これら三つのルートにおける成果を個別に見ていく。

GPU、FPGA、ASIC

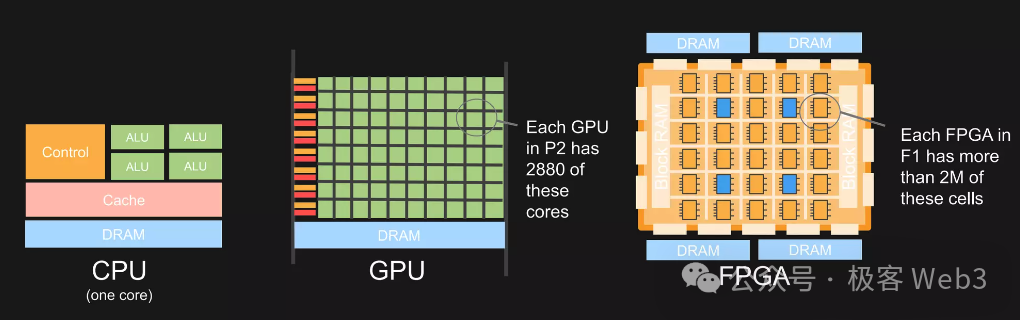

ZKハードウェアアクセラレーションの核心は、重要な計算を可能な限り並列化することにある。ハードウェアの機能特性から見ると、CPUは最大限の柔軟性と汎用性を実現するために、チップ面積の大部分を制御機能とキャッシュに割いており、並列計算能力は弱い。

一方、GPUでは計算に使用されるチップ面積の比率が大幅に増加しており、大規模な並列処理をサポートできる。現在、GPUは非常に普及しており、Nvidia CUDAなどのライブラリにより、開発者は底層ハードウェアを知らなくても並列性を利用できる。CUDA SDKを通じてCUDA ZKライブラリをパッケージ化し、MSMおよびNTT演算を高速化できる。

FPGAは多数の小型処理ユニットからなるアレイであり、プログラミングには専用のハードウェア記述言語を使用し、トランジスタ回路の組み合わせにコンパイルする必要がある。つまり、FPGAは命令セットを介さず、直接トランジスタ回路で特定のアルゴリズムを実装する。このカスタマイズ性と柔軟性はGPUをはるかに超える。

現在、FPGAの価格はGPUのおよそ3分の1であり、エネルギー効率はGPUを10倍以上上回る。この顕著な効率の優位性の一因は、GPUがホスト機器に接続する必要があり、通常ホスト機器が大量の電力を消費するためである。つまり、FPGAはエネルギー消費を増加させずに、MSMおよびNTTのニーズに対応するための計算モジュールを追加できる。これにより、計算密度が高く、高スループットかつ低遅延が求められるZK証明シナリオに特に適している。

しかし、FPGA最大の問題は、プログラミング経験を持つ開発者が極めて少ないことである。ZKプロジェクトにとって、暗号学の専門知識とFPGAエンジニアリングの専門知識を兼ね備えたチームを編成することは極めて困難である。

一方、ASICは特定のプログラムを完全にハードウェアで実装したものであり、設計完了後はハードウェアの変更が不可能であり、実行できるプログラムも変更できないため、特定タスク専用となる。前述のFPGAがMSMおよびNTTで示すハードウェアアクセラレーションの利点は、ASICも同様に備えている。専用回路設計ゆえに、ASICはすべてのソリューションの中で最も高性能かつ最低消費電力である。

現在の主流ZK Circuitにおいて、Cysicは証明時間を1〜5秒にまで短縮することを目指しており、この目標を達成するにはASICしか手段がない。

これらの利点は非常に魅力的に聞こえるが、ZK技術は急速に進化しており、ASICの設計・製造サイクルは通常1〜2年かかり、コストは1000万〜2000万ドルに達する。したがって、ZK技術が十分に安定するまで待つ必要があり、製造されたチップがすぐに陳腐化するリスクを避ける必要がある。

このため、GPU、FPGA、ASICの三領域において、Cysicは十分な準備をしている。

GPUアクセラレーションソリューションに関しては、さまざまな新型ZK証明システムの登場に合わせ、Cysicは自社開発のCUDAアクセラレーションSDKでそれらを適応させ、コミュニティリソースを結集することで、CysicのGPU計算ネットワークに数十万枚のトップクラスGPUをリンクさせた。また、CysicのCUDA SDKは最新のオープンソースフレームワークよりも50〜80%以上高速である。

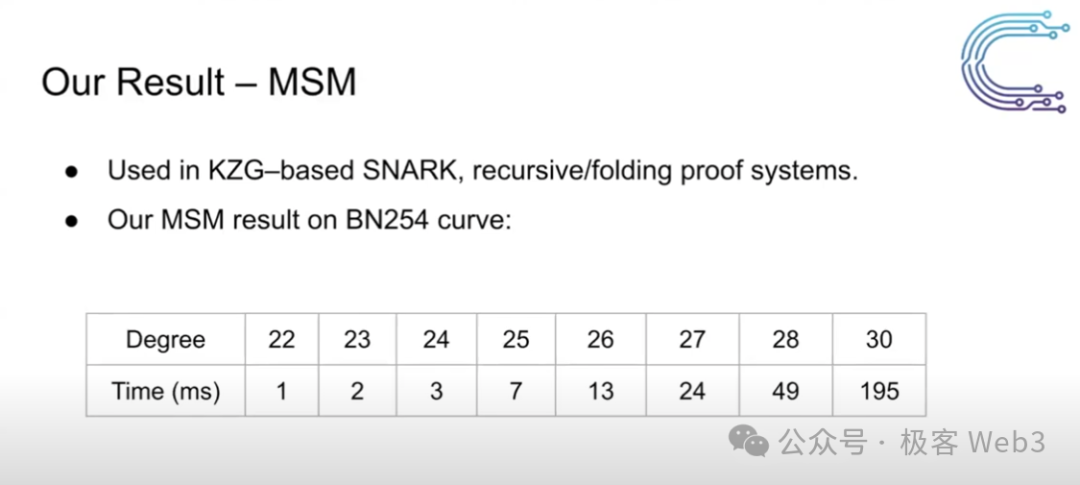

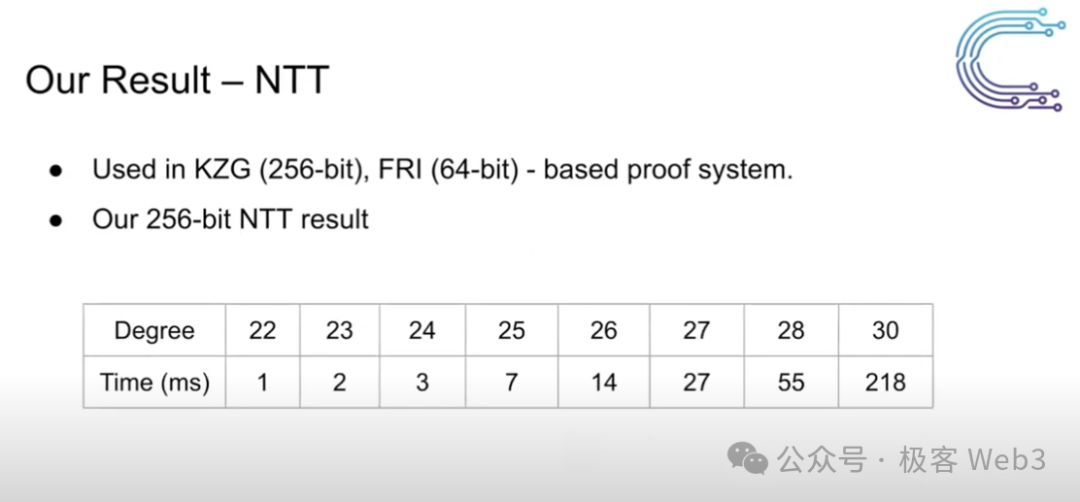

FPGAにおいては、自社開発ソリューションにより、世界最速のMSM、NTT、Poseidon Merkle treeモジュールを実現し、ZK計算の主要部分をカバーした。このソリューションは複数のトップZKプロジェクトでプロトタイプ検証を経ている。

Cysicが独自開発したSolarMSMは、2^30規模のMSM計算を0.195秒で完了でき、SolarNTTは同じ規模のNTT計算を0.218秒で完了する。これは現時点で公開されているすべてのFPGAハードウェアアクセラレーション結果の中で最高性能である。

ASIC分野においても、ZK ASICの大規模適用まではまだ距離があるが、Cysicはすでにこの分野に早期から参入しており、独自開発のZK DePINチップおよびデバイスをリリースしている。

C端ユーザーを惹きつけ、異なるZKプロジェクトの性能とコスト要件を満たすため、Cysicは二種類のZKハードウェア製品をリリースする予定:ZK AirおよびZK Proである。

ZK AirはモバイルバッテリーやノートPCのACアダプタほどの大きさで、一般ユーザーはType-CケーブルでノートPC、iPad、あるいはスマホに直接接続でき、特定のZKプロジェクトに計算リソースを提供して報酬を得られる。現在のZK Airの計算能力はすでにコンシューマー向けGPUを超え、小規模なZK証明生成を加速できる。

ZK Proは従来のマイニングマシンに似ており、複数のハイエンドコンシューマーGPUを接続したサーバーと同等の計算能力を持ち、ZK証明生成を大幅に加速できる。ZK-RollupやZKML(ゼロナレッジマシンラーニング)といった大規模ZKプロジェクトに適している。

この二つのデバイスを通じて、Cysicは最終的に安定かつ信頼できるZK-DePINネットワークを構築する。現在、これらのデバイスは開発中であり、2025年の上市が予定されている。

さらに、Cysic Networkを通じて、C端ユーザーは非常に低いハードルでZKハードウェアアクセラレーション市場に参加できる。ZKプロジェクトからの強大な計算需要もあり、ビットコインマイニングのようなブームが再び起きる可能性があり、ZK計算分野の市場規模は爆発的な成長を遂げるかもしれない。

TechFlow公式コミュニティへようこそ

Telegram購読グループ:https://t.me/TechFlowDaily

Twitter公式アカウント:https://x.com/TechFlowPost

Twitter英語アカウント:https://x.com/BlockFlow_News